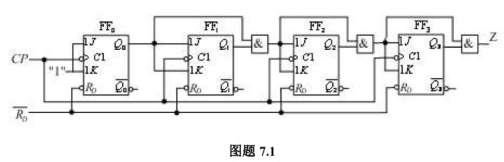

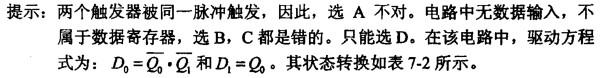

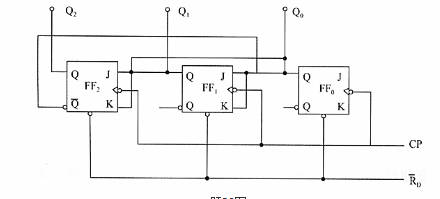

计数器电路如图题7.1所示。设各触发器的初始状态均为“0”,分析该电路的逻辑功能。

第1题:

第2题:

第3题:

第4题:

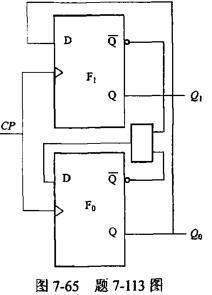

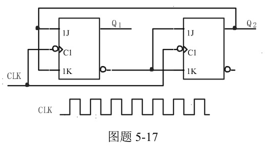

试画出图题5-17所示电路中触发器输出Q1、Q2 端的波形,CLK 的波形如图所示。(设Q初始状态为0)

第5题:

试画出图题5-19所示电路中触发器输出Q1、Q2端的波形,输入端CLK的波形如图所示。(设Q初始状态为0)

第6题:

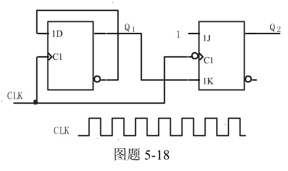

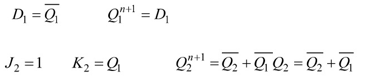

试画出图题5-18所示电路中触发器输出Q1、Q2端的波形,CLK的波形如图所示。(设Q初始状态为0)

第7题:

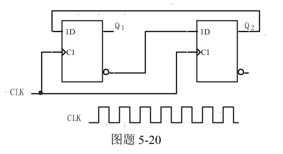

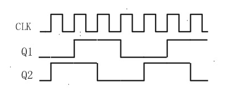

试画出图题5-20所示电路中触发器输出Q1、Q2端的波形,CLK的波形如图所示。(设Q初始状态为0)

第8题:

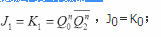

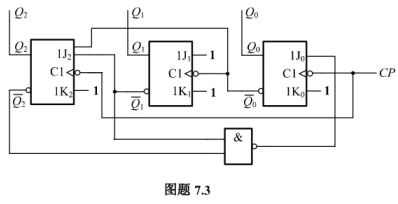

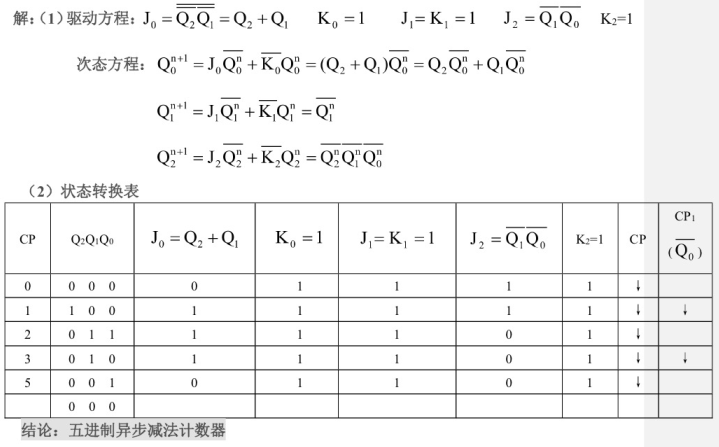

计数器电路如图题7.3所示。设各触发器的初始状态均为“0”,要求:

(1) 写出各触发器的驱动方程和次态方程;

(2)画出次态卡诺图;画出状态转换图并说明该计数器电路的逻辑功能;

第9题:

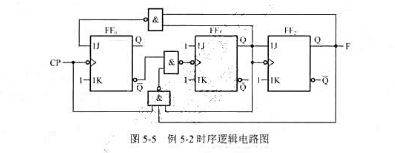

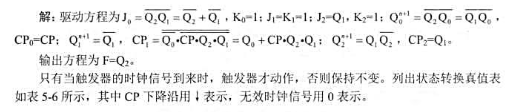

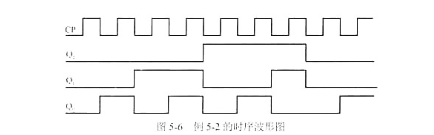

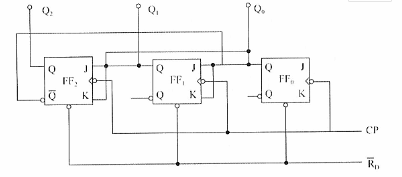

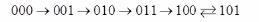

时序逻辑电路如图5-5所示,分析电路的功能,写出驱动方程,状态方程,列出状态转换真值表,画出Q2Q1Q0时序波形和状态转换图,说明电路的功能,是否能自启动.假设初始状态为000.