解析:

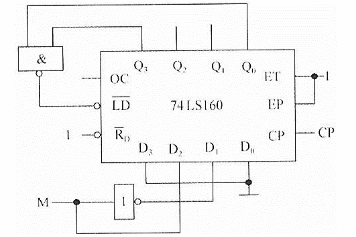

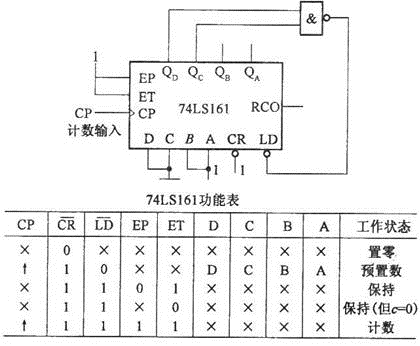

74LS160为同步十进制计数器,当为低电平时,将D3、D2、D1、D0置入计数器。当M=1时,初始值为0100,计数器根据CP脉冲开始计数,0100→0101→0110→0111→1000→1001,当计数到1001时Q3和Q0经与非门使得LD=0,则计数器将初始值0100置数到输出端,进行下一轮计数,因此当M=1时为六进制计数器。当M=0时,初始值为0010,计数器根据CP脉冲开始计数,0010→0011→0100→0101→0110→0111→1000→1001,当计数到1001时Q3和Q0经与非门使得,则计数器将初始值0010置数到输出端,继续进行下一轮计数,因此当M=0时为八进制计数器。