第1题:

●DQDB同时支持 (33) 两种服务。DQDB子网的双总线结构由 (34) 总线以及接在这两条总线上的大量的节点组成。DQDB网络为双总线提供了 (35) 访问控制方式,其中能够提供非等时服务是 (36) ,它用于 (37) 业务。

(33) A.电路交换和信元交换

B.虚电路交换和分组交换

C.电路交换和分组交换

D.报交电路交换和分组交换

(34) A.一条双向

B.一条单向

C.两条双向

D.两条单向

(35) A.时分多址访问和预先仲裁访问

B.预先仲裁和排队仲裁访问

C.载波监听多路访问和排队仲裁访问

D.排队仲裁访问和令牌总线

(36) A.预先仲裁访问

B.时分多址访问

C.排队仲裁访问

D.载波监听多路访问

(37) A.电路交换

B.分组交换

C.信元交换

D.虚电路交换

第2题:

第3题:

此题为判断题(对,错)。

第4题:

简述PCI总线的仲裁机制。

第5题:

CAN总线仲裁的原则和原理是什么?

第6题:

在嵌入式处理器中,下面关于“菊花链”仲裁的叙述,错误的是(29) 。

A.菊花链仲裁又称为串行仲裁

B.菊花链仲裁使用三根控制线:总线请求线、总线允许线和总线忙线

C.在菊花链模式下,总线允许线连接的先后次序决定了每个模块的优先级

D.在菊花链模式下,每一时刻可以有多个模块作为总线通信的实际主控模块

第7题:

ISA总线需要进行总线仲裁吗?为什么?

第8题:

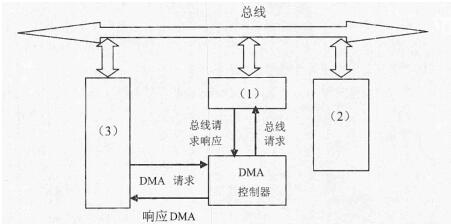

文中( 3 )处正确的答案是( )。

A.时分多址访问和预先仲裁访问

B.预先仲裁和排队仲裁访问

C.载波监听多路访问和排队仲裁访问

D.排队仲裁访问和令牌总线

第9题:

什么情况下需要总线仲裁?总线仲裁的目的是什么?有哪几种常用的仲裁方式?各有什么特点?

第10题:

总线数据传输为什么要进行总线仲裁?