第1题:

某二进制数字串共有15位,其中的数字1共有四个连续子串,从左到右依次有1、5、3、2位,各子串之间都至少有1个数字0。例如,101111101110011、100111110111011都是这种二进制数字串。因此可推断,该种数字串中一定是1的位共有( )位。

A.7 B.8C.9 D.1 1

第2题:

第3题:

64位的安腾处理器为了达到最高的指令级的并行性,采用了最新设计理念,EPIC的全称是【 】。

第4题:

并行处理机也称()计算机,是一种SIMD,采用资源重复并行性。

第5题:

从处理数据的角度,并行性等级可以分为字串位串、()、()、和全并行。

第6题:

第7题:

从执行程序的角度看,并行性等级从低到高可分为哪几级?

第8题:

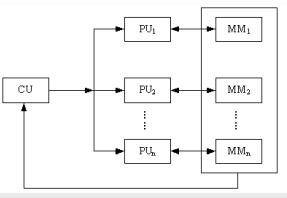

● 某计算机系统的结构如下图所示,按照弗林(Michael J.Flynn)提出的分类法,它属于 (17) ,其中,PUi(i=1,…,n)为处理单元,CU为控制部件,MM j(j=1,…,n)为存储部件。该计算机 (18) 。

(17)

A. 单指令流单数据流计算机(SISD)

B. 单指令流多数据流计算机(SIMD)

C. 多指令流单数据流计算机(MISD)

D. 多指令流多数据流计算机(MIMD)

(18)

A. 通过时间重叠实现并行性

B. 通过资源重复实现并行性

C. 通过资源共享实现并行性

D. 通过精简指令系统实现并行性

第9题:

开发并行性是为了并行处理,并行性又包括有()和并发性二重含义。

第10题:

多处理机是(),与并行性处理机的本质差别是并行性级别不同。多处理机实现任务作业一级的并行,而并行处理机只实现指令一级并行。