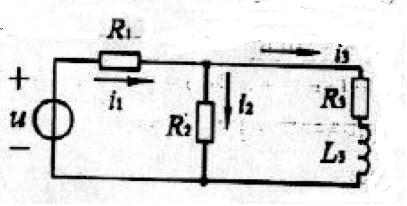

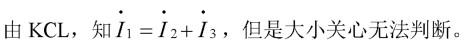

当t=0°时,i1、i2、i3分别为()。

第1题:

当发生两相接地短路时,短路点故障分量I1、I2、I0的关系是()。

A、I1=I2=I0;

B、I1=-I2-I0;

C、I0=I1+I2;

第2题:

A.0、负值、正值

B.0、正值、负值

C.负值、0、正值

D.负值、正值、0

第3题:

A、超前Π/4rad

B、滞后3Π/4rad

C、滞后Π/4rad

D、超前3Π/4rad

第4题:

第5题:

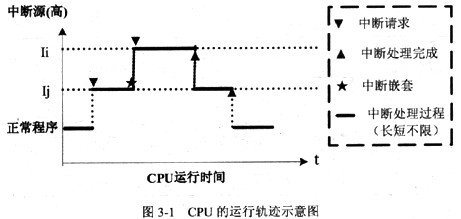

阅读以下关于中断的叙述,回答问题1至问题3,将答案填入对应栏内。

【说明】

某计算机中断系统有4级中断I1,I2,I3和I4,中断响应的优先次序为I1→I2→I3→I4,即先响应I1,冉响应I2,……,最后响应I4。每级中断对应一个屏蔽码,屏蔽码中某位为“1”表示禁止中断(关中断),若为“0”则表示允许中断(开中断)。各级中断处理程序与屏蔽码的关系如表3-1所示。

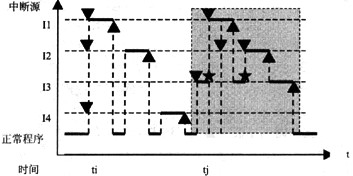

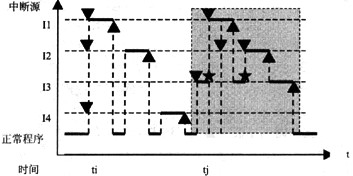

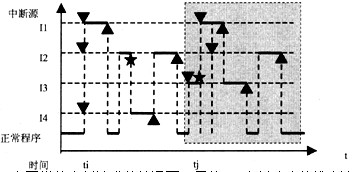

若ti时刻I1、I2和I4级同时产生中断,在各中断处理完成后,tj(ti<tj)时刻发出I3

级中断申请,CPU为I3服务时,I1级发出请求,在CPU为I1服务时,I2级发出请求。请参照图3-1所示的格式,画出CPU的运行轨迹。

解析:本题考查的是中断基础知识,中断是计算机中一个非常重要的概念,在嵌入式计算机中的应用极为广泛。采用中断的优点是既能提高CPU的效率又能对突发事件作出实时处理。考生需要正确理解中断的概念,了解中断处理过程,包括中断请求、中断响应、中断处理如中断返回。同时还要正确理解中断的优先级概念,CPU对各中断级的处理一般原则是;

解析:本题考查的是中断基础知识,中断是计算机中一个非常重要的概念,在嵌入式计算机中的应用极为广泛。采用中断的优点是既能提高CPU的效率又能对突发事件作出实时处理。考生需要正确理解中断的概念,了解中断处理过程,包括中断请求、中断响应、中断处理如中断返回。同时还要正确理解中断的优先级概念,CPU对各中断级的处理一般原则是;第6题:

电路中,流进节点A的电流分别为I1,I2,流出节点A的电流为I3,据( )定律,可得节点A的电流为I1+I2=I3。

A.基尔霍夫第二

B.基尔霍夫第一

C.电流

D.电压

第7题:

若i1=10sin(314t+90°),i2=10sin(314t-90°),i3=10sin314t,其单位是A,当它们通过同一电阻,且通电时间相等时,发热量最大的是( )。

A.i1

B.i2

C.i3

D.三者相等

第8题:

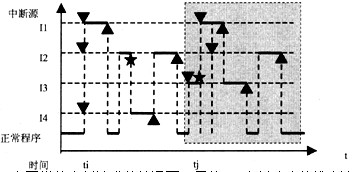

设中断优先次序为I1→I4→I3→I2。若ti时刻I1、I2和I4级同时产生中断,在各中断处理完成后,tj(ti<tj)时刻发出I3级中断申请,CPU为I3服务时,I1级发出请求,在CPU为I1服务时,I2级发出请求。请画出这种情况下CPU的运行轨迹。

解析:在同样的中断请求的情况下,尽管CPU中断响应的优先次序不变(I1→I2→I3→I4),但是由于中断屏蔽码不同,CPU的运行轨迹发生了变化,详见参考答案。其中ti时刻I1、 I2和I4三个请求同时到达,CPU首先响应I1级请求,紧接着响应I2级请求,但是I2级的屏蔽吗是对I4级开放的,当I2级的程序执行到开中断指令时,立即被I4级中断,CPU转去执行I4级程序,待服务完毕后,再返回处理I2级。如果忽略上述细节,也可简单的画出CPU按I1、I4和I2的处理次序执行。在tj时刻,CPU处理完I4级程序后,I3级发出申请,CPU响应并为其服务。在为I3级服务的过程中,又来了I1级请求,I3级可被I1级中断,故CPU转为I1级服务。在CPU为I1级服务的过程中,I2级发出申请,但因I2级的处理级别最低,故CPU不理睬I2级的请求,直至I3级服务完毕,再响应I2级请求。本题主要考查考生对多重中断处理的理解,在画CPU处理轨迹时,可以画回到正常程序,也可以不画回到正常程序。

解析:在同样的中断请求的情况下,尽管CPU中断响应的优先次序不变(I1→I2→I3→I4),但是由于中断屏蔽码不同,CPU的运行轨迹发生了变化,详见参考答案。其中ti时刻I1、 I2和I4三个请求同时到达,CPU首先响应I1级请求,紧接着响应I2级请求,但是I2级的屏蔽吗是对I4级开放的,当I2级的程序执行到开中断指令时,立即被I4级中断,CPU转去执行I4级程序,待服务完毕后,再返回处理I2级。如果忽略上述细节,也可简单的画出CPU按I1、I4和I2的处理次序执行。在tj时刻,CPU处理完I4级程序后,I3级发出申请,CPU响应并为其服务。在为I3级服务的过程中,又来了I1级请求,I3级可被I1级中断,故CPU转为I1级服务。在CPU为I1级服务的过程中,I2级发出申请,但因I2级的处理级别最低,故CPU不理睬I2级的请求,直至I3级服务完毕,再响应I2级请求。本题主要考查考生对多重中断处理的理解,在画CPU处理轨迹时,可以画回到正常程序,也可以不画回到正常程序。

第9题:

试题三(共 20 分)

阅读以下关于中断的叙述,回答问题 1 至问题 3,将答案填入答题纸的对应栏内。

【说明】

某计算机中断系统有 4级中断 I1,I2,I3 和I4,中断响应的优先次序为 I1→I2→I3→I4,即先响应 I1,再响应 I2,……,最后响应 I4。每级中断对应一个屏蔽码,屏蔽码中某位为“1”表示禁止中断(关中断) ,若为“0”则表示允许中断(开中断) 。各级中断处理程序与屏蔽码的关系如表 3-1 所示。

【问题 1】 (6 分)

若ti 时刻I1、I2 和 I4 级同时产生中断,在各中断处理完成后,tj(ti<tj)时刻发出 I3 级中断申请,CPU 为 I3 服务时,I1 级发出请求,在 CPU 为 I1 服务时,I2 级发出请求。请参照图 3-1 所示的格式,画出CPU的运行轨迹。

【问题 2】 (8 分)

若将中断优先次序设置为 I1→I4→I3→I2,即先响应 I1,再响应 I4,……,最后响应 I2。请重新设置各级的屏蔽码,填写表 3-2。

【问题 3】 (6 分)

设中断优先次序为 I1→I4→I3→I2。若 ti 时刻 I1、I2 和 I4 级同时产生中断,在各中断处理完成后,tj(ti<tj)时刻发出 I3 级中断申请,CPU为 I3服务时,I1级发出请求,在 CPU为 I1 服务时,I2 级发出请求。请画出这种情况下 CPU的运行轨迹。

第10题: